| CPU12                                                                         | The CPU12 Central Processing Unit          |

|-------------------------------------------------------------------------------|--------------------------------------------|

|                                                                               | M68HC12 and HCS12 microcontrollers         |

| Babak Kia<br>Adjunct Professor<br>Boston University<br>College of Engineering |                                            |

| Email: bkia -at- bu.edu                                                       | ENG SC757 - Advanced Microprocessor Design |

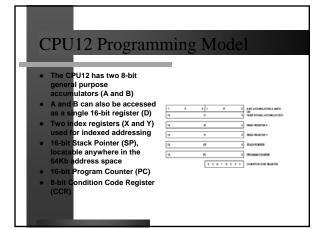

# CPU12 Programming Model

- The Condition Code Register consists of 5 status indicators, 2 interrupt masks, and a STOP instruction control bit

- S Control Bit. Clearing the S bit enables the STOP instruction which stops the on-chip oscillator. If set, the CPU treats the STOP instruction as a NOP.

- Set, the GFD heats the offer manufacture as a roof is X Mask Bit. The XIRQ# signal poses as a motified version of the NMI# interrupt. Enabling a nonmaskable interrupt before a system is fully operational can lead to spurious interrupts. The X bit allows for the enabling of the NMI once the custom is constrained.

- system is operational • *H Status Bit.* The H bit indicates a half-carry on the accumulator. It is used by the DAA instruction on BCD operations

## **CPU12** Programming Model

- I Mask Bit. The I bit enables or disables all maskable interrupts. The I bit is set to 1 (masked) at reset. While I is set, interrupts can become pending and are remembered, but the system is not interrupted until the I mask is cleared.

- N Status Bit. The N bit is mostly used in two's complement arithmetic and shows the state of the MSB of the result.

- Z Status Bit. Z is set when the result of an operation is 0.

- V Status Bit. V is the overflow indicator.

- C Status Bit. C is set when carry occurs during an addition, or a borrow is needed during subtraction.

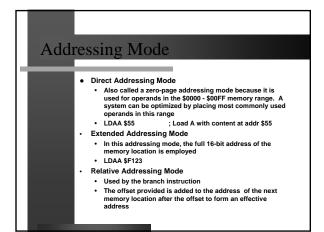

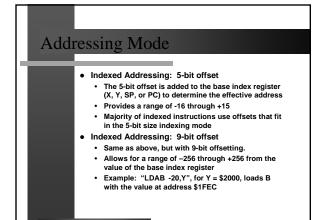

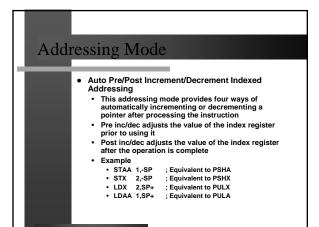

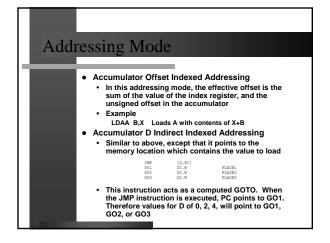

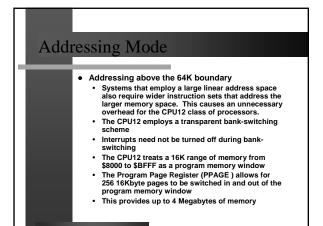

### Addressing Mode • The CPU12 employs an extensive Addressing Mode scheme: Inherent Indexed (accumulator Immediate offset) • Indexed (9-bit offset) Direct • Indexed (16-bit offset) Extended • Indexed-Indirect (16- Relative bit offset) • Indexed (5-bit offset) • Indexed-Indirect (D • Indexed (pre-dec.) accumulator offset) • Indexed (pre-inc.) • Indexed (post-dec.) · Indexed (post-inc.)

|         | ·                |                                                                                                         |

|---------|------------------|---------------------------------------------------------------------------------------------------------|

| Address | ing Mod          | e                                                                                                       |

|         |                  |                                                                                                         |

| • Ini   | nerent Addressi  | ng Mode                                                                                                 |

| ·       |                  | t use this addressing mode either<br>ds, or the operands are CPU                                        |

| •       | NOP              | ; Does not have an operand                                                                              |

| •       | INX              | ; Operand is a CPU register                                                                             |

| • Im    | mediate Addres   | ssing Mode                                                                                              |

| ·       | present during r | mediate Addressing mode are<br>normal program fetch cycle. The '#'<br>to identify the immediate operand |

| •       | LDAA #\$55       | ; Load A with 8-bit value                                                                               |

| •       | LDX #\$1234      | ; Load X register with 16-bit value                                                                     |

|         |                  |                                                                                                         |

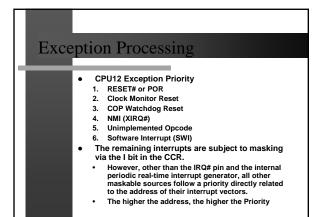

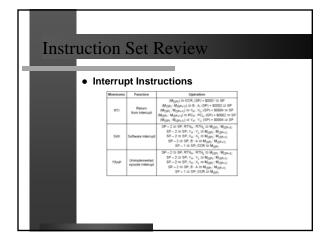

### **Exception Processing**

- The CPU12 has several sources of Interrupts

Reset

- Power-on Reset (POR) and RESET#

- Clock Monitor Reset

- COP Watchdog Reset

- Unimplemented Opcode Trap

- Software Interrupt Instruction (SWI)

- Non Maskable Interrupt (X-bit)

- Non Maskable Interrupt (I-bit)

- The CPU12 can handle up to 128 exception vectors, but the number varies with each device

| Encention | Duc            |                                             |  |

|-----------|----------------|---------------------------------------------|--|

| Exception | I Proc         | essing                                      |  |

|           |                | 5                                           |  |

|           |                |                                             |  |

|           |                |                                             |  |

| • CPU     | J12 Exce       | ption Vector Map                            |  |

|           |                | · · · ·                                     |  |

|           | Vector Address | Source                                      |  |

|           | SHLE-SHLE      | System reset                                |  |

|           | SFFFC-SFFFD    | Clock monitor reset                         |  |

|           | SFFFA-SFFFB    | COP reset                                   |  |

|           | SFFF8-SFFF9    | Unimplemented opcode trap                   |  |

|           | SFFF6-SFFF7    | Software interrupt instruction (SWI)        |  |

|           | SFFF4-SFFFS    | XIRQ signal                                 |  |

|           | SFFF2-SFFF3    | TRIC signal                                 |  |

|           | \$FF00-\$FFF1  | Device-specific interrupt sources (HCS12)   |  |

|           | SFFC0-SFFF1    | Device-specific interrupt sources (M68HC12) |  |

|           |                |                                             |  |

|           |                |                                             |  |

|           |                |                                             |  |

|           |                |                                             |  |

|           |                |                                             |  |

|           |                |                                             |  |

|           |                |                                             |  |

|           |                |                                             |  |

|           |                |                                             |  |

|           |                |                                             |  |

|           |                |                                             |  |

|           |                |                                             |  |

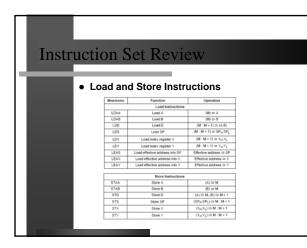

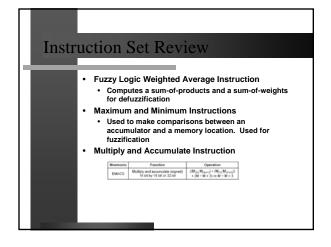

| Instruct | tion      | Set Re                           | view                                                           |       |

|----------|-----------|----------------------------------|----------------------------------------------------------------|-------|

| msuuci   |           | bet Re                           | VIEW                                                           |       |

|          |           |                                  | _                                                              |       |

|          |           |                                  |                                                                |       |

|          | Tranefor  | and Eve                          | hange Instruct                                                 | ione  |

| •        | inalisiei |                                  | nange manuer                                                   | 10115 |

|          | Mnemonic  | Function                         | Operation                                                      |       |

|          |           | Transfer In                      | structions                                                     |       |

|          | TAB       | Transfer A to B                  | (A) ⇒ B                                                        |       |

|          | TAP       | Transfer A to CCR                | (A) ⇒ CCR                                                      |       |

|          | TBA       | Transfer B to A                  | (B) ID A                                                       |       |

|          | TFR       | Transfer register<br>to register | (A, B, CCR, D, X, Y, or SP) ⇒<br>A, B, CCR, D, X, Y, or SP     |       |

|          | TPA.      | Transfer CCR to A                | $(CCR) \Rightarrow A$                                          |       |

|          | TSX       | Transfer SP to X                 | $(5P) \Rightarrow X$                                           |       |

|          | TSY       | Transfer SP to V                 | (5P) ⇒ Y                                                       |       |

|          | TXS       | Transfer X to SP                 | (X) => SP                                                      |       |

|          | Tr'S      | Transfer Y to SP                 | (Y) ⇒ SP                                                       |       |

|          |           | Exchange I                       | netructions                                                    |       |

|          | EXG       | Exchange register<br>to register | (A, B, CCR, D, X, Y, or SP) (0)<br>(A, B, CCR, D, X, Y, or SP) |       |

|          | XGDX      | Exchange D with X                | $(0) \oplus (0)$                                               |       |

|          | XGDV      | Exchange D with Y                | $(0) \oplus (1)$                                               |       |

|          |           | Sign Extensio                    | n Instruction                                                  |       |

|          | SEX       | Sign extend<br>8-Bit operand     | Sign-extended (A, B, or CCR) ⇒<br>D, X, Y, or SP               |       |

|          |           |                                  |                                                                |       |

|          |           |                                  |                                                                |       |

|          |           |                                  |                                                                |       |

|          |           |                                  |                                                                |       |

Г

|                                    | Set Rev                                                              |                                                                                                                            |

|------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

|                                    |                                                                      |                                                                                                                            |

|                                    |                                                                      |                                                                                                                            |

| Move In:                           | structions                                                           |                                                                                                                            |

| Mnemonic                           | Function                                                             | Operation                                                                                                                  |

| MOV8                               | Move byte (8-bit)                                                    | $(M_s) \Rightarrow M_s$                                                                                                    |

| MOVW                               | Move word (16-bit)                                                   | $(M:M+1_{*}) \supset M:M+1_{*}$                                                                                            |

| Binary C                           | oded Instr                                                           | uctions                                                                                                                    |

| Binary C                           | Coded Instr                                                          | ructions                                                                                                                   |

| -                                  |                                                                      |                                                                                                                            |

| Mnemonic                           | Function                                                             | Operation                                                                                                                  |

| Mnemonic<br>ABA                    | Function<br>Add B to A                                               | Operation<br>(A) = (B) $\Rightarrow$ A                                                                                     |

| Mnemonic<br>ABA<br>ADCA            | Function<br>Add 8 to A<br>Add with cerry to A                        | Operation<br>$(A) = (B) \Rightarrow A$<br>$(A) + (M) + C \Rightarrow A$                                                    |

| ABA<br>ADCA<br>ADCB <sup>(1)</sup> | Function<br>Add 8 to A<br>Add with carry to A<br>Add with carry to 8 | $\begin{array}{c} \text{Operation} \\ (A) \circ (B) \cong A \\ (A) + (M) + C \cong A \\ (B) + (M) + C \cong B \end{array}$ |

|                         |         | ч. <b>р</b> . •              |                                   |        |

|-------------------------|---------|------------------------------|-----------------------------------|--------|

| nstructio               | n N     | Set Revi                     | ew                                |        |

| moti detto              | 11 1    |                              |                                   |        |

|                         |         |                              |                                   |        |

| _                       |         |                              |                                   |        |

| امام م                  |         |                              | ation Instant                     |        |

| <ul> <li>Add</li> </ul> | itioi   | n and Subtra                 | iction instru                     | ctions |

|                         | nemonic | Function                     | Operation                         |        |

|                         |         | Addition Instruction         |                                   |        |

|                         | ABA     | A of 8 to A                  | $(A) + (B) \supset A$             |        |

|                         | ABX     | Add 8 to X                   | (B) + (X) = X                     |        |

|                         | ABY     | Add 8 to Y                   | $(B) + (Y) \Rightarrow Y$         |        |

|                         | ADCA    | Add with carry to A          | $(A) + (M) + C \Longrightarrow A$ |        |

|                         | ADC8    | Add with carry to 8          | $(B) + (M) + C \implies B$        |        |

|                         | ADDA    | Add without carry to A       | $(A) + (M) \Longrightarrow A$     |        |

|                         | ADDB    | Add without carry to B       | $(B) + (M) \Rightarrow B$         |        |

|                         | ADDD    | Add to D                     | $(A:B) + (M:M+1) \Rightarrow A:B$ |        |

|                         |         | Subtraction Instructi        | ons                               |        |

|                         | 58A     | Subtract 8 from A            | (A) – (B) ⇒ A                     |        |

|                         | SBCA    | Subtract with borrow from A  | $(A) = (M) = C \Longrightarrow A$ |        |

|                         | 5808    | Subtract with borrow from B  | $(B) = (M) = C \Longrightarrow B$ |        |

|                         | SUBA    | Subtract memory from A       | $(A)=(M) \Longrightarrow A$       |        |

|                         | \$U88   | Subtract memory from B       | $(B) - (M) \equiv B$              |        |

|                         | SUBD    | Subtract memory from D (A:B) | $(D) = (M : M + 1) \Rightarrow D$ |        |

|                         |         |                              |                                   |        |

|                         |         |                              |                                   |        |

|                         |         |                              |                                   |        |

.

|       | a                           | ( D ·                 |                           |          |

|-------|-----------------------------|-----------------------|---------------------------|----------|

| istru | action S                    | et Kevi               | ew                        |          |

|       |                             |                       |                           |          |

|       |                             |                       |                           |          |

|       |                             |                       |                           |          |

|       | <ul> <li>Decreme</li> </ul> | nt and Incre          | ement Insti               | ructions |

|       |                             |                       |                           |          |

|       | Mnemonic                    | Function              | Operation                 | 1        |

|       |                             | Decrement Instruction |                           | 1        |

|       | DEC                         | Decrement memory      | (M) – 501 ⇒ M             | 1        |

|       | DECA                        | Decrement A           | (A) – 501 ⇒ A             | 1        |

|       | DEC8                        | Decrement 8           | (8) = \$01 ⇒ 8            | 1        |

|       | DES                         | Decrement SP          | (SP) - \$0001 ⇒ SP        | 1        |

|       | DEX                         | Decrement X           | (X) – \$0001 ⇒ X          | 1        |

|       | DEY                         | Decrement V           | (Y) = \$0001 ⇒ Y          | 1        |

|       |                             | Increment Instructio  |                           | 1        |

|       | INC                         | Increment memory      | $(M) + $01 \Rightarrow M$ |          |

|       | INCA                        | Increment A           | (A) + \$01 ⇒ A            |          |

|       |                             | increment B           | (B) + \$01 ⇒ B            | 1        |

|       | INC8                        |                       |                           |          |

|       | INS                         | Increment SP          | (SP) + \$0001 ⇒ SP        | 1        |

|       |                             |                       |                           | -        |

| ion 9    | Set Revie                     | 137               |

|----------|-------------------------------|-------------------|

|          |                               | / <b>V V</b>      |

|          |                               |                   |

|          |                               |                   |

| omnar    | e and Test Ins                | struction         |

| ompu     | o una root me                 |                   |

| Mnemonic | Function                      | Operation         |

|          | Compare Instructions          |                   |

| CBA      | Compare A to B                | (A) – (B)         |

| CMPA     | Compare A to memory           | (A) = (M)         |

| CMPB     | Compare B to memory           | (B) = (B)         |

| CPD      | Compare D to memory (16-bit)  | (A:B) = (M:M+1)   |

| CPS      | Compare SP to memory (16-bit) | (SP) - (M: M+1)   |

| CPX.     | Compare X to memory (16-bit)  | (X) = (M : M + 1) |

| CPY      | Compare Y to memory (16-bit)  | (1) = (M:M+1)     |

|          | Test Instructions             |                   |

| TST      | Test memory for zero or minus | (M) = \$00        |

|          | Test A for zero or minus      | (A) - \$00        |

| TSTA     |                               |                   |

| Instructi | on (     | Set Review                             | <b>X</b> 7                                                         |  |

|-----------|----------|----------------------------------------|--------------------------------------------------------------------|--|

| msuucu    |          |                                        | vv                                                                 |  |

|           |          |                                        |                                                                    |  |

|           |          |                                        |                                                                    |  |

|           |          |                                        | •                                                                  |  |

| • Bo      | olear    | n Logic Instruct                       | lions                                                              |  |

|           | Mnemonic | Function                               | Operation                                                          |  |

|           | ANDA     | AND A with memory                      | (A) + (M) ⇒ A                                                      |  |

|           | ANDB     | AND 8 with memory<br>AND 8 with memory | $(A) \bullet (M) \Rightarrow A$<br>$(B) \bullet (M) \Rightarrow B$ |  |

|           | ANDCC    | AND CCR with memory (clear CCR bits)   | (0)*(M) = 0<br>(CCR)*(M) = CCR                                     |  |

|           | EORA     | Exclusive OR A with memory             | $(A) \oplus (M) \Rightarrow A$                                     |  |

|           | EORB     | Exclusive OR B with memory             | $(0) \oplus (M) \Rightarrow 0$                                     |  |

|           | ORAA     | OR A with memory                       | $(0) \oplus (0) \Rightarrow 0$<br>$(A) + (M) \Rightarrow A$        |  |

|           | ORAB     | OR 8 with memory                       | $(n) + (m) \Rightarrow n$<br>$(0) + (M) \Rightarrow 0$             |  |

|           | ORCC     | OR CCR with memory (set CCR bits)      | $(O) + (M) \Rightarrow CCR$                                        |  |

|           | 01100    | or contact the target of the contact   | (000) - (4) - 000                                                  |  |

| • Bit     |          | & Manipulation                         |                                                                    |  |

|           | Mnemon   | ic Function                            | Operation                                                          |  |

|           | BCLR     | Clear bits in memory                   | $(M) \bullet (\overline{mm}) \Rightarrow M$                        |  |

|           | BITA.    | Bit test A                             | (A) • (M)                                                          |  |

|           | BITB     | Bit test B                             | (B) • (M)                                                          |  |

|           | 8SET     | Set bits in memory                     | $(M) + (mm) \Longrightarrow M$                                     |  |

|          |          | _                       |                                                                            |  |

|----------|----------|-------------------------|----------------------------------------------------------------------------|--|

| Instruct | ion (    | Set Rev                 | iew                                                                        |  |

| mouuci   | 10IL     | JULINU                  |                                                                            |  |

|          |          |                         |                                                                            |  |

|          |          |                         |                                                                            |  |

|          |          |                         |                                                                            |  |

| • (      | Clear. C | complemen               | t, and Negate                                                              |  |

|          |          | •                       | ., <b>.</b>                                                                |  |

|          | nstruct  | lions                   |                                                                            |  |

|          |          |                         |                                                                            |  |

|          | Mnemonic | Function                | Operation                                                                  |  |

|          | CLC      | Clear C bit in CCR      | 0 = C                                                                      |  |

|          | CLI      | Clear I bit in CCR      | 0 = 1                                                                      |  |

|          | CLR      | Clear memory            | \$00 ⇒ M                                                                   |  |

|          | CLRA     | Clear A                 | \$00 ⇒ A                                                                   |  |

|          | CLRB     | Ciear 8                 | \$00 ⇒ 8                                                                   |  |

|          | CLV      | Clear V bit in COR      | 0 => V                                                                     |  |

|          | COM      | One's complement memory | $SFF - (M) \cong M \text{ or } (\overline{M}) \cong M$                     |  |

|          | COMA     | One's complement A      | $SFF - (A) \Longrightarrow A \text{ or } (\overline{A}) \Longrightarrow A$ |  |

|          | COMB     | One's complement B      | $FF - (B) \Rightarrow B \text{ or } (\overline{B}) \Rightarrow B$          |  |

|          | NEG      | Two's complement memory | $SOO = (M) \Rightarrow M \text{ or } (\overline{M}) + 1 \Rightarrow M$     |  |

|          | NEGA     | Two's complement A      | \$00 - (A) ID A or (A) + 1 ID A                                            |  |

|          | NEGB     | Two's complement B      | $SOO = (B) \Rightarrow B \text{ or } (\overline{B}) + 1 \Rightarrow B$     |  |

|          |          |                         |                                                                            |  |

|          |          |                         |                                                                            |  |

|          |          |                         |                                                                            |  |

|          |          |                         |                                                                            |  |

|          |          |                         |                                                                            |  |

|       | tion C    | at Dessier                         |                                                            |

|-------|-----------|------------------------------------|------------------------------------------------------------|

| struc | tion S    | et Review                          | N                                                          |

|       |           |                                    |                                                            |

|       |           |                                    |                                                            |

| •     | Multiplic | ation and Divis                    | sion Inst                                                  |

|       | Mnemonic  | Function                           | Operation                                                  |

|       |           | Multiplication Instructions        |                                                            |

|       | EMUL      | 16 by 16 multiply (unsigned)       | $(D) \times (Y) \Rightarrow Y : D$                         |

|       | EMULS     | 16 by 16 multiply (signed)         | $(D) \times (Y) \Rightarrow Y : D$                         |

|       | MUL       | 8 by 8 multiply (unsigned)         | $(A) \times (B) \Rightarrow A : B$                         |

|       |           | Division Instructions              |                                                            |

|       | EDIV      | 32 by 16 divide (unsigned)         | $(Y : D) + (X) \Rightarrow Y$<br>Remainder $\Rightarrow D$ |

|       | EDIV'S    | 32 by 16 divide (signed)           | (Y : D) + (X) ⇒ Y<br>Remainder ⇒ D                         |

|       | FDIV      | 16 by 16 fractional divide         | (D) + (X) ⇒ X<br>Remainder ⇒ D                             |

|       | ID!//     | 16 by 16 integer divide (unsigned) | (D) + (R) ID X<br>Remainder ⇒ D                            |

|       | ID1//S    | 16 by 16 integer divide (signed)   | $(D) + (X) \Rightarrow X$<br>Remainder $\Rightarrow D$     |

| structio  | on                   | Set Re                                                                                            | view                   |

|-----------|----------------------|---------------------------------------------------------------------------------------------------|------------------------|

| Stituette | 511                  |                                                                                                   | 1011                   |

|           |                      |                                                                                                   | l                      |

| • Sh      | ift a                | nd Rotate I                                                                                       | nstruction             |

| • 011     | Maemonia             |                                                                                                   |                        |

|           | Mnemonic             | Function<br>Logical Shifts                                                                        | Operation              |

|           | LSL<br>LSLA<br>LSLB  | Logic shift left memory<br>Logic shift left A<br>Logic shift left 8                               | 6-turnin -             |

|           | LSLD                 | Logic shift left D                                                                                | 6-0110-0110-           |

|           | LSR<br>LSRA<br>LSRB  | Logic shift right memory<br>Logic shift right A<br>Logic shift right B                            | é- <del>duund</del> -ó |

|           | LSRD                 | Logic shift right D                                                                               | ⇔arina•brina•b         |

|           |                      | Arithmetic Shi                                                                                    | ta .                   |

|           | ASL<br>ASLA<br>ASLB  | Anthreeic shift left memory<br>Anthreeic shift left A<br>Anthreeic shift left S                   | ó• <del>duunð</del> ⊷  |

|           | ASLD                 | Autometic shift left D                                                                            | ó-trift-triff-         |

|           | ASRA<br>ASRA         | Arithmetic shift right memory<br>Arithmetic shift right A<br>Arithmetic shift right B             | ¢-û                    |

|           |                      | Rotates                                                                                           |                        |

|           | ROL<br>ROLA<br>ROLB  | Rotate left memory through carry<br>Rotate left A through carry<br>Rotate left 8 through carry    | رەقتىتىتە-ئ-           |

|           | RORA<br>RORA<br>RORB | Rotate right memory through carry<br>Rotate right A through carry<br>Rotate right B through carry | Gamming-0-2            |

|   | Instr | uction                                            | n Set R                                   | Review                                                                                                                                                                                                                                   |                       |

|---|-------|---------------------------------------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Ī |       | <ul> <li>Int<br/>me</li> <li>An<br/>se</li> </ul> | erpolate val<br>emory.<br>ly function v   | ition Instructions<br>ues from tables sto<br>vhich can be repres<br>r equations can be<br>i                                                                                                                                              | red in<br>sented as a |

|   |       | Mner                                              | monic Function                            | Operation                                                                                                                                                                                                                                | 1                     |

|   |       | e                                                 | BL (no indirect addressing modes allowed) | $\begin{array}{c} (M:M+1)+  B )\times ((M+2:M+3)\\ -(M:M+1)  B  \gg D\\ \\ \text{Initialize B, and index before ETBL,}\\ \text{reav points to the first lable entry }(M:M=1)\\ B \text{ is fractional part of lookup value} \end{array}$ |                       |

|   |       | -                                                 | BL (no indirect addressing modes allowed) | $\begin{array}{l} (M)+[(0)\times((M+1)-(M)([(\supset A \\ initialize [0, and index before TBL.\\  points to the first 0-bit table entry (M)  B is fractional part of lookup value. \end{array}$                                          |                       |

|   |       |                                                   |                                           |                                                                                                                                                                                                                                          | <i>.</i>              |

| Tre atoms at: | ~          | C at D                                                  |            |                             |  |

|---------------|------------|---------------------------------------------------------|------------|-----------------------------|--|

| Instruction   | on         | Set K                                                   | ev         | iew                         |  |

|               | ~          | 20011                                                   | • •        | 10                          |  |

|               |            |                                                         |            |                             |  |

|               |            |                                                         |            |                             |  |

|               |            |                                                         | _          |                             |  |

| e Sh          | ort E      | Branch Ins                                              |            | otiona                      |  |

| • 30          |            |                                                         | suu        |                             |  |

|               | Maemonic   | Function                                                |            | Equation or Operation       |  |

|               | Mnemonic   | Unary Bran                                              | ihee.      | Equation or Operation       |  |

|               | B/RA       | Branch elezys                                           | 2508       | 141                         |  |

|               | DEN        | Branch never                                            |            | 1+0                         |  |

|               |            | Single Fran                                             | -then      |                             |  |

|               | BCC        | Branch if came clear                                    |            | C+0                         |  |

|               | BCS        | Branch if carry set                                     |            | C+1                         |  |

|               | 860        | Branch if equal                                         |            | Z+1                         |  |

|               | GMI        | Branch if minus                                         |            | N=1                         |  |

|               | BNE        | Branch if not equal                                     |            | Z = 0                       |  |

|               | 825        | Branch if plue                                          |            | N = 0                       |  |

|               | BVC.       | Branch if overflow cies                                 |            | V = 0                       |  |

|               | 81/5       | Branch if overfow set                                   |            | V = 1                       |  |

|               |            | Unsigned Bra                                            |            |                             |  |

|               |            |                                                         | Relation   |                             |  |

|               | Brt        | Branch if higher                                        | R>M        | C+2+0                       |  |

|               | BHS<br>BLO | Branch if higher or same<br>Branch if isseer            | R1M<br>R1M | C=0<br>C=1                  |  |

|               | BLD<br>BLS | Branch / lower                                          |            |                             |  |

|               | 0.5        | Branch if lower or same<br>Signed Bran                  | R≦M        | C+2+1                       |  |

|               | POE        | Branch If greater than or equal                         | RUM        | N#V+0                       |  |

|               | BOE        | Branch / greater than or equal<br>Branch / greater than | 8.18       | 2+ (10/01+0                 |  |

|               | BUE        | Branch / greater than<br>Branch / seas than or equal    | RIM        | 2+ (N 0 V)+0<br>2+(N 0 V)+1 |  |

|               | 8.7        | Branch if less than                                     | R-M        | N#V=1                       |  |

|               |            |                                                         |            |                             |  |

|               |            |                                                         |            |                             |  |

|               |            |                                                         |            |                             |  |

| _          |              |                                                 |                       |  |

|------------|--------------|-------------------------------------------------|-----------------------|--|

| Instructio | n            | Sot Dour                                        | OW                    |  |

|            |              |                                                 | CW                    |  |

|            |              |                                                 |                       |  |

|            |              |                                                 |                       |  |

|            |              |                                                 |                       |  |

|            |              |                                                 |                       |  |

| - L        | ~ D          | ranah Inatru                                    | tiono                 |  |

| • Lon      | yь           | ranch Instru                                    | Juons                 |  |

|            | -            |                                                 |                       |  |

| E          | hemonic      | Function                                        | Equation or Operation |  |

|            |              | Unary Branches                                  |                       |  |

|            | LBRA         | Long branch always                              | 1+1                   |  |

|            | LBRN         | Long branch never                               | 1+0                   |  |

|            |              | Simple Branches                                 |                       |  |

|            | LBCC         | Long branch if carry clear                      | C = 0                 |  |

|            | LBCS         | Long branch if carry set                        | C=1<br>Z=1            |  |

|            | LBEQ         | Long branch if equal<br>Long branch if minus    | 2=1<br>N=1            |  |

|            | LENE         | Long branch if minus                            | 2=0                   |  |

|            | LEVE         | Long branch if not equal<br>Long branch if plus | 2=0<br>N=0            |  |

|            | LEVC         | Long tranch if overflow clear                   | V+0                   |  |

|            | LBVC<br>LBVS | Long branch if overflow set                     | V=0<br>V=1            |  |

| -          | LBYD         | Unsigned Branches                               | ,                     |  |

|            | Liter        | Long branch if higher                           | C+Z+0                 |  |

|            | LBHS         | Long branch if higher or same                   | C+0                   |  |

|            | LBLO         | Long branch if lower                            | 2+1                   |  |

|            | LBLS         | Long branch if lower or same                    | C+Z+1                 |  |

|            |              | Signed Branches                                 |                       |  |

|            | LEOE         | Long branch if greater than or equal            | NeV-0                 |  |

|            | LBGT         | Long branch if greater than                     | 2+0(0)0+0             |  |

|            | LELE         | Long branch if less than or equal               | Z=0(0))=1             |  |

|            | LALT         | Long branch if less than                        | N#V=1                 |  |

|            |              |                                                 |                       |  |

|            |              |                                                 |                       |  |

| ructi                   | on       | Set Revi                                                                                                                                       | ew                                                                                                                                                                        |

|-------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ucu                     | on       |                                                                                                                                                |                                                                                                                                                                           |

|                         |          |                                                                                                                                                |                                                                                                                                                                           |

|                         |          |                                                                                                                                                |                                                                                                                                                                           |

| <ul> <li>Bit</li> </ul> | Cor      | dition Branc                                                                                                                                   | h Instructio                                                                                                                                                              |

|                         | Mnemoni  | e Function                                                                                                                                     | Equation or Operation                                                                                                                                                     |

|                         | BRCLR    | Branch if selected bits clear                                                                                                                  | (M) • (mm) = 0                                                                                                                                                            |

|                         | BRSET    | Branch if selected bits set                                                                                                                    | (M) • (mm) = 0                                                                                                                                                            |

|                         | Mnemonic | Function                                                                                                                                       | Equation or Operation                                                                                                                                                     |

|                         | 0850     | Decrement counter and branch if = 0<br>(counter = A, B, D, X, Y, or SP)                                                                        | (counter) = 1⇒ counter<br>If (counter) = 0, then branch;<br>else continue to next instruction                                                                             |

|                         | DBNE     | Decrement counter and branch if # 0<br>(counter = A, B, D, X, Y, or SP)                                                                        | (counter) = 1⇒ counter<br>If (counter) not = 0, then branch;<br>else continue to next instruction                                                                         |

|                         | 1860     | Increment counter and branch if = 0<br>(counter = A, B, D, X, Y, or SP)                                                                        | (counter) + 110 counter<br>If (counter) = 0, then branch;<br>else continue to next instruction                                                                            |

|                         | IBNE     | increment counter and branch if # 0<br>(counter = A, B, D, X, Y, or SP)                                                                        | (counter) + 1= counter<br>If (counter) not = 0, then branch;<br>else continue to next instruction                                                                         |

|                         | TREO     | Test counter and branch if = 0<br>(counter = A. B. D. X.Y. or SP)                                                                              | If (counter) = 0, then branch;<br>else continue to next instruction                                                                                                       |

|                         | 100.0    | (sources = A, 0, 0, A, 1, 0, 0+)                                                                                                               | File comments in their mercerore                                                                                                                                          |

|                         | IBNE     | (souriter = A, B, D, X, Y, or SP)<br>Increment counter and branch if = 0<br>(counter = A, B, D, X, Y, or SP)<br>Test counter and branch if = 0 | else continue to next instruction<br>(counter) + 1:> counter<br>If (counter) not = 0, then branch;<br>else continue to next instruction<br>If (counter) = 0, then branch; |

| a at was a | tion (   |                                       |                                                                                                                                                                                                                                                                                                      |

|------------|----------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| struc      | 110N S   | Set Rev                               | view                                                                                                                                                                                                                                                                                                 |

|            |          |                                       |                                                                                                                                                                                                                                                                                                      |

|            |          |                                       |                                                                                                                                                                                                                                                                                                      |

| •          | Jump ar  | nd Subrou                             | tine Instructi                                                                                                                                                                                                                                                                                       |

|            | Mnemonic | Function                              | Operation                                                                                                                                                                                                                                                                                            |

|            | BSR      | Branch to subroutine                  | SP = 2 $\Rightarrow$ SP<br>RTN <sub>H</sub> : RTN <sub>L</sub> $\Rightarrow$ M <sub>(SP)</sub> : M <sub>(SP-1</sub> )<br>Subroutine address $\Rightarrow$ PC                                                                                                                                         |

|            | CALL     | Call subroutine<br>in expanded memory | $\begin{array}{c} SP = 2 \ensuremath{\boxtimes}\ SP = 2 \ensuremath{\boxtimes}\ SP \\ RTN_{41}(RTN_{12} \Rightarrow M_{(SP)}) \colon M_{(SP-1)} \\ SP = 1 \ensuremath{\cong}\ SP \\ (PPAGE) \Rightarrow M_{(SP)} \\ Page \ensuremath{\cong}\ PPAGE \\ Subroutine address \Rightarrow PC \end{array}$ |

|            | JMP      | qmuG                                  | Address ⇒ PC                                                                                                                                                                                                                                                                                         |

|            | JSR      | Jump to subroutine                    | $\begin{array}{l} SP=2 \Rightarrow SP\\ RTN_{kc}\colon RTN_{k} \supseteq M_{(SP)}\colon M_{(SP-1)}\\ Subroutine address \Rightarrow PC \end{array}$                                                                                                                                                  |

|            | RTC      | Return from call                      | $\begin{array}{c} M_{(SP)} \Rightarrow PPAGE\\ SP+1 \Rightarrow SP\\ M_{(SP)}: M_{(SP+1)} \Rightarrow PC_H: PC_L\\ SP+2 \Rightarrow SP \end{array}$                                                                                                                                                  |

|            | RTS      | Return from subroutine                | $M_{(SP)}: M_{(SP_{n}1)} \Rightarrow PC_{H}: PC_{L}$<br>$SP + 2 \Rightarrow SP$                                                                                                                                                                                                                      |

|        | Set R                          |                                                                |

|--------|--------------------------------|----------------------------------------------------------------|

| ICHON  | NOT R                          | eview                                                          |

|        | DULIN                          |                                                                |

|        |                                |                                                                |

|        |                                |                                                                |

|        |                                |                                                                |

|        |                                |                                                                |

|        |                                |                                                                |

|        | Manipula                       | tion Instr                                                     |

|        | wampula                        | lion man                                                       |

|        |                                |                                                                |

| Mnemon |                                | Operation                                                      |

|        | Addition Instruc               |                                                                |

| 481    | Add 8 to X                     | (#1+(X)=X                                                      |

| ×8×    | AM 8 to Y                      | $(B) + (Y) \Rightarrow Y$                                      |

|        | Compare tratruc                |                                                                |

| CPS    | Compare SP to memory           | (SP) = (M : M = 1)                                             |

| CPX    | Compare X to memory            | (1) = (M M + 1)                                                |

| CPV    | Compare Y to memory            | $(V) = (M \cdot M + 1)$                                        |

|        | Load Instructs                 | ina                                                            |

| 1.05   | Load SP from memory            | W W-1 10 5P                                                    |

| 4.D.X  | Load X from memory             | (M M + 1) = X                                                  |

| LÓV    | Load 1 from memory             | (M   M + 1) = Y                                                |

| LEAS   | Load effective address into SP | Effective address to 5P                                        |

| LEAS   | Load effective address into X  | Effective address to X                                         |

| UEAT   | Load effective address into Y  | Effective address to V                                         |

|        | Store Instruction              | orius.                                                         |

| \$75   | Stare SP in memory             | (SP) => M(M+1)                                                 |

| 57X    | Store X in memory              | (C) 10-M M = 1                                                 |

| 57V    | Store 7 in memory              | (7) IP M   M + 1                                               |

|        | Stateby Instruc                | Done                                                           |

| 378    | Transfer register to register  | 0A, B, COR, D, X, Y, or SP)<br>10 A, B, COR, D, X, Y, or SP    |

| 75×    | Transfer SP to X               | (5P) to X                                                      |

| 757    | Transfer SP to V               | (SP) = Y                                                       |

| 7×3    | transfer X to SP               | 00.02.5P                                                       |

| Tra    | transfer 7 to 5P               | (0) IP 5P                                                      |

|        | Exchange instru                |                                                                |

| EXG    | Exchange register to register  | (A, B, COR, D, X, Y, or SP)<br>(0) (A, B, COR, D, X, Y, or SP) |

| ×66×   | Exchange D with X              | 01000                                                          |

| 1007   | Exchange C with Y              | (0) (0)                                                        |

|        |                                |                                                                |

|             |                      | ~                                    | <b>-</b> ·                                                                                                                                                        |

|-------------|----------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Instruction | on                   | Sot                                  | PAULAW                                                                                                                                                            |

| insu ucu    | υII                  | DCL.                                 | NEVIEW                                                                                                                                                            |

|             | -                    |                                      |                                                                                                                                                                   |

|             |                      |                                      |                                                                                                                                                                   |

|             |                      |                                      |                                                                                                                                                                   |

|             |                      |                                      |                                                                                                                                                                   |

| - Ct        |                      |                                      | rustions                                                                                                                                                          |

| • 36        | acki                 | ng insi                              | ructions                                                                                                                                                          |

|             |                      | •                                    |                                                                                                                                                                   |

|             | Mnemonic             | function                             | Operation                                                                                                                                                         |

|             |                      |                                      | ter instructions                                                                                                                                                  |

|             | 095                  | Compare SP to memory                 | (SP) = (M : M + 1)                                                                                                                                                |

|             | OE5<br>INS           | Decrement SP<br>Increment SP         | (5P) = 1 ID 5P<br>(5P) + 1 ID 5P                                                                                                                                  |

|             | 015                  | Load SP                              | (SP)+1 ID SP<br>(N N+1) ID SP                                                                                                                                     |

|             |                      | Linki effective address              |                                                                                                                                                                   |

|             | LEAS                 | into SP                              | Effective address to SP                                                                                                                                           |

|             | 575                  | Store SP                             | (SP) => M : M + 1                                                                                                                                                 |

|             | 75×                  | Tranafor SP to X                     | (5P) 10 X                                                                                                                                                         |

|             | 151                  | Transfer SP to Y                     | (5P) = Y                                                                                                                                                          |

|             | TX5                  | Transfer X to SP<br>Transfer X to SP | (0) 10 SP<br>(0) 10 SP                                                                                                                                            |

|             | 115                  |                                      | (7) IP 3P<br>ation Instructions                                                                                                                                   |

|             | PONA                 | Back Open                            | (SP) = 1 = SP; (A) = M <sub>15P</sub> .                                                                                                                           |

|             | PSH8                 | Putri A                              | (SP) = 1 = SP, (0) = M <sub>SP</sub>                                                                                                                              |

|             | PSHC                 | Public CR                            | (P) - 1 = SP. (A) = Man                                                                                                                                           |

|             | PIHO                 | Push COR                             | $(SP) = 1 \Rightarrow SP, (A) \Rightarrow M_{(SP)}$<br>$(SP) = 2 \Rightarrow SP, (A, B) \Rightarrow M_{(SP)}, M_{(SP,1)}$                                         |

|             | PSHX                 | Puero<br>Puero                       | (SP) = 2 ID SP, (A. B) ID M((P), M((P+1))<br>(SP) = 2 ID SP, (A) ID M((P, 1))                                                                                     |

|             | PSHX                 | Puen X<br>Puen Y                     | $(SP) = 2 \oplus SP, (1) \oplus M_{(SP)}; M_{(SP+1)}$<br>$(SP) = 2 \oplus SP, (1) \oplus M_{(SP)}; M_{(SP+1)}$                                                    |

|             |                      |                                      |                                                                                                                                                                   |

|             | PULA                 | PylA                                 | $(M_{(p)}) \equiv h_{1}(SP) + 1 \equiv SP$                                                                                                                        |

|             | PULB                 | Pulb                                 | $(M_{(S^p)}) \simeq 0; (S^p) = 1 \simeq S^p$                                                                                                                      |

|             | PULC                 | Put CCR                              | (M(pP) II) CCR, (SP) + 1 III SP                                                                                                                                   |

|             |                      |                                      |                                                                                                                                                                   |

|             | PULD                 | Pull D                               | $(M_{(S^P)}:M_{(S^P,r)}) \cong A: \mathbb{R}, (S^P)*2 \cong S^P$                                                                                                  |

|             | PULD<br>PULX<br>PULX | Pul D<br>Pul X<br>Pul X              | $(M_{(2P)}, M_{(2P-1)}) \cong X, (2P) + 2 \cong 2P$<br>$(M_{(2P)}, M_{(2P-1)}) \cong X, (2P) + 2 \cong 2P$<br>$(M_{(2P)}, M_{(2P-1)}) \cong Y, (2P) + 2 \cong 2P$ |

| Instructio | on       | Set F                                                                                            | Revie                                                                                                                | W                                                                                                                                                                                                                                                                                 |             |  |

|------------|----------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| • Po       | inter    |                                                                                                  | dex Cal                                                                                                              |                                                                                                                                                                                                                                                                                   | nstructions |  |

|            | LEAS     | Load result of indexed addressing mode                                                           |                                                                                                                      | r ± constant to SP or<br>(r) + (accumulator) to SP<br>r + X, Y, SP, or PC                                                                                                                                                                                                         |             |  |

|            | LEAX     | Load result of indexed addressing mode<br>effective address calculation<br>into x index register |                                                                                                                      | $r \pm \text{constant} \Rightarrow X \text{ or}$<br>(r) + (accumulator) $\Rightarrow X$<br>r = X, Y, SP,  or PC                                                                                                                                                                   |             |  |

|            | LEAY     | effective addr                                                                                   | ied addressing mode<br>ress calculation<br>lex register                                                              | $\label{eq:relation} \begin{array}{l} r \pm \text{constant} \rightrightarrows Y \text{ or} \\ (r) + (accumulator) \rightrightarrows Y \\ r + X, Y, SP, \text{ or PC} \end{array}$                                                                                                 |             |  |

| • Sto      | op an    | d Wait                                                                                           | Instruc                                                                                                              | tions                                                                                                                                                                                                                                                                             |             |  |

|            | Mnemonic | Function                                                                                         | 0                                                                                                                    | peration                                                                                                                                                                                                                                                                          | 1           |  |

|            | STOP     | Stop                                                                                             | $SP - 2 \Rightarrow SP; Y_i$<br>$SP - 2 \Rightarrow SP; X_i$<br>$SP - 2 \Rightarrow SP; 8$<br>$SP - 1 \Rightarrow 3$ | $\begin{array}{l} _{k}(RDk_{i} \cong M_{(SP_{i})}) : M_{(SP_{i},1)} \\ _{k}(Y_{k} \cong M_{(SP_{i})}) : M_{(SP_{i},1)} \\ _{k}(X_{k} \cong M_{(SP_{i})}) : M_{(SP_{i},1)} \\ _{k}(SP_{i}) : M_{(SP_{i},1)} \\ \\ (P, CCR \cong M_{(SP_{i})}) \\ CPU \ docks \end{array}$          |             |  |

|            | WAI      | Wait for interrupt                                                                               | $SP = 2 \Rightarrow SP; Y$<br>$SP = 2 \Rightarrow SP; X$<br>$SP = 2 \Rightarrow SP; 8$                               | $\begin{array}{l} (:RTH_{L} \Rightarrow M_{(SP)}:M_{(SP-1)} \\ (:Y_{L} \Rightarrow M_{(SP)}:M_{(SP-1)} \\ (:X_{L} \Rightarrow M_{(SP)}:M_{(SP-1)} \\ (:X_{L} \Rightarrow M_{(SP)}:M_{(SP-1)} \\ (:A \Rightarrow M_{(SP)}:M_{(SP-1)} \\ (:P, CCR \Rightarrow M_{(SP)} \end{array}$ |             |  |

|            |          |                                                                                                  |                                                                                                                      |                                                                                                                                                                                                                                                                                   |             |  |

|  | _ |

|--|---|

|  |   |

|  |   |

|  |   |

|  |   |

|  |   |

|  |   |

|  | _ |

|  |   |

|  |   |

|  |   |

|  |   |

|  |   |

|  |   |

|  | _ |

|  |   |

|  |   |

|  |   |

|  |   |

|  |   |

|  |   |

|  | _ |

|  |   |

|  |   |

|  |   |

|  |   |

|  |   |

|  |   |

|  |   |

|  |   |

| <b>T</b> 4 |                             |                             | •                                                           |   |

|------------|-----------------------------|-----------------------------|-------------------------------------------------------------|---|

| Instr      | liction :                   | Set Rev                     | 1ew                                                         |   |

| Inou       | action                      |                             | 10 11                                                       | r |

|            |                             |                             |                                                             |   |

|            |                             |                             |                                                             |   |

|            | <b>A</b> 11/1               | <b>•</b> • •                |                                                             |   |

|            | <ul> <li>Conditi</li> </ul> | on Code Ins                 | tructions                                                   |   |

|            |                             |                             |                                                             |   |

|            | Mnemonic                    | Function                    | Operation                                                   |   |

|            | ANDCC                       | Logical AND CCR with memory | $(CCR) \bullet (M) \Rightarrow CCR$                         |   |

|            | CLC                         | Clear C bit                 | 0 ⇒ C                                                       |   |

|            | cu                          | Clear   bit                 | 0 10 1                                                      |   |

|            | CLV.                        | Clear V bit                 | 0 -> V                                                      |   |

|            | ORCC                        | Logical OR CCR with memory  | $(CCR) + (M) \Rightarrow CCR$                               |   |

|            | PSHC                        | Push CCR onto stack         | $(SP) = 1 \Rightarrow SP; (CCR) \Rightarrow M_{(SP)}$       |   |

|            | PULC                        | Pull CCR from stack         | $(M_{(SP)}) \Rightarrow CCR; (SP) + 1 \Rightarrow SP$       |   |

|            | SEC                         | Set C bit                   | 1 = C                                                       |   |

|            | 581                         | Set i bit                   | 1 -> 1                                                      |   |